Структура памяти напоминает таблицу, где сначала выбирают строку, а затем столбец. Эта таблица разбита на банки, для памяти плотностью меньше 64Мбит (SDRAM) количеством 2 штуки, выше - 4 (стандартно). Спецификация память DDR2 SDRAM с чипами плотностью 1Гбит предусматривает уже 8 банков. На открытие строки в используемом банке уходит больше времени, нежели в другом (т.к. используемую строку нужно сначала закрыть). Очевидно, что лучше новую строку открывать в новом банке (на этом основан принцип чередования строк).

Обычно на памяти (или в спецификации к ней) есть надпись вида 3-4-4-8 или 5-5-5-15. Это сокращенная запись (так называемая схема таймингов) основных таймингов памяти. Что же такое тайминги? Очевидно, что ни одно устройство не может работать с бесконечной скоростью. Значит, на выполнение любой операции уходит какое-либо время. Тайминги - это задержка, устанавливающая время, необходимое на выполнение какой-либо команды, то есть время от отправки команды до ее выполнения. А каждая цифра обозначает какое именно время необходимо.

Теперь разберем каждый по очереди. Схема таймингов включает в себя задержки CL-Trcd-Trp-Tras соответственно. Для работы с памятью необходимо для начала выбрать чип, с которым мы будем работать. Делается это командой CS# (Chip Select). Затем выбирается банк и строка. Перед началом работы с любой строкой необходимо ее активировать. Делается это командой выбора строки RAS# (при выборе строки она активируется). Затем (при операции линейного чтения) нужно выбрать столбец командой CAS# (эта же команда инициирует чтение). Затем считать данные и закрыть строку, совершив предварительный заряд (precharge) банка.

Тайминги расположены по порядку следования в простейшем запросе (для простоты понимания). Сначала идут тайминги, затем подтайминги.

Trcd, RAS to CAS delay - время, необходимое для активизации строки банка, или минимальное время между подачей сигнала на выбор строки (RAS#) и сигнала на выбор столбца (CAS#).

CL, Cas Latency - минимальное время между подачей команды на чтение (CAS) и началом передачи данных (задержка чтения).

Tras, Active to Precharge - минимальное время активности строки, то есть минимальное время между активацией строки (ее открытием) и подачей команды на предзаряд (начало закрытия строки). Строка не может быть закрыта раньше этого времени.

Trp, Row Precharge - время, необходимое для предварительного заряда банка (precharge). Иными словами, минимальное время закрытия строки, после чего можно активировать новую строку банка.

CR, Command Rate 1/2T - Время, необходимое для декодирования контроллером команд и адресов. Иначе, минимальное время между подачей двух команд. При значении 1T команда распознается 1 такт, при 2T - 2 такта, 3T - 3 такта (пока только на RD600).

Это все основные тайминги. Остальные тайминги имеют меньшее влияние на производительность, а потому их называют подтаймингами.

Trc, Row Cycle Time, Activate to Activate/Refresh Time, Active to Active/Auto Refresh Time - минимальное время между активацией строк одного банка. Является комбинацией таймингов Tras+Trp - минимального времени активности строки и времени ее закрытия (после чего можно открывать новую).

Trfc, Row Refresh Cycle Time, Auto Refresh Row Cycle Time, Refresh to Activate/Refresh Command Period - минимальное время между командой на обновление строки и командой активизации, либо другой командой обновления.

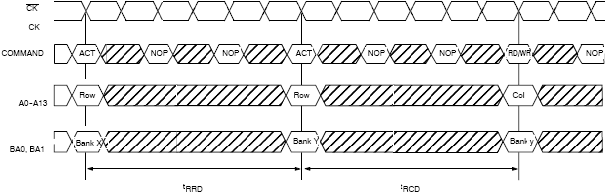

Trrd, ACTIVE bank A to ACTIVE bank B command, RAS to RAS Delay, Row Active to Row Active - минимальное время между активацией строк разных банков. Архитектурно открывать строку в другом банке можно сразу за открытием строки в первом банке. Ограничение же чисто электрическое - на активацию уходит много энергии, а потому при частых активациях строк очень высока электрическая нагрузка на цепи. Чтобы ее снизить, была введена данная задержка. Используется для реализации функции чередования доступа к памяти (interleaving).

Tccd, CAS to CAS Delay - минимальное время между двумя командами CAS#.

Twr, Write Recovery, Write to Precharge - минимальное время между окончанием операции записи и подачей команды на предзаряд (Precharge) строки для одного банка.

Twtr</B>, Trd_wr, Write To Read - минимальное время между окончанием записи и подачей команды на чтение (CAS#) в одном ранке.

RTW, Read To Write, (Same) Rank Read To Write - минимальное время между окончанием операции чтения и подачей команды на запись, в одном ранке.

Same Rank Write To Write Delayed - минимальное время между двумя командами на запись в одном ранке.

Different Rank Write to Write Delay - минимальное время между двумя командами на запись в разных ранках.

Twr_rd, Different Ranks Write To READ Delayed - минимальное время между окончанием записи и подачей команды на чтение (CAS#) в разных ранках.

Same Rank Read To Read Delayed - минимальная задержка между двумя командами на чтение в одном ранке.

Trd_rd, Different Ranks Read To Read Delayed - минимальная задержка между двумя командами на чтение в разных ранках.

Trtp, Read to Precharge - минимальный интервал между подачей команды на чтение до команды на предварительный заряд.

Precharge to Precharge - минимальное время между двумя командами предварительного заряда.

Tpall_rp, Precharge All to Active Delay - задержка между командой Precharge All и командой на активацию строки.

Same Rank PALL to REF Delayed - устанавливает минимальное время между командой Precharge All и Refresh в одном ранке.

Different Rank REF to REF Delayed - устанавливает минимальную задержку между двумя командами на обновление (refresh) в разных ранках.

Twcl, Write Latency - задержка между подачей команды на запись и сигналом DQS. Аналог CL, но для записи.

Tdal, цитата из JEDEC 79-2C, p.74: auto precharge write recovery + precharge time (Twr+Trp).

Trcd_rd/Trcd_wr, Activate to Read/Write, RAS to CAS Read/Write Delay, RAW Address to Column Address for Read/Write - сочетание двух таймингов - Trcd (RAS to CAS) и rd/wr command delay. Именно последним и объясняется существование разных Trcd - для записи и чтения (Nf2) и установки BIOS - Fast Ras to Cas.

Tck, Clock Cycle Time - период одного такта. Именно он и определяет частоту памяти. Считается она следующим образом: 1000/Tck=X Mhz (реальная частота).

CS, Chip Select - время, необходимое на выполнения команды, подаваемой сигналом CS# для выбора нужного чипа памяти.

Tac, DQ output access time from CK - время от фронта такта до выдачи данных модулем.

Address and Command Setup Time Before Clock - время, на которое передача установок адресов команд будет предшествовать восходящему фронту такта.

Address and Command Hold Time After Clock - время, на которое будут "заперты" установки адреса и команд после нисходящего фронта такта.

Data Input Setup Time Before Clock, Data Input Hold Time After Clock - то же, что и вышеуказанные, но для данных.

Tck max, SDRAM Device Maximum Cycle Time - максимальный период цикла устройства.

Tdqsq max, DDR SDRAM Device DQS-DQ Skew for DQS and associated DQ signals - максимальный сдвиг между стробом DQS и связанными с ним сигналами данных.

Tqhs, DDR SDRAM Device Read Data Hold Skew Factor - максимальный сдвиг "запирания" считанных данных.

Tch, Tcl, CK high/low pulse width - длительность высокого/низкого уровня тактовой частоты CK.

Thp, CK half pulse width - длительность полупериода тактовой частоты CK.

Max Async Latency - максимальное время асинхронной задержки. Параметр управляет длительностью асинхронной задержки, зависящей от времени, необходимого для передачи сигнала от контроллера памяти до самого дальнего модуля памяти и обратно. Опция существует в процессорах компании AMD (Athlon/Opteron).

DRAM Read Latch Delay- задержка, устанавливающая время, необходимое для "запирания" (однозначного распознавания) конкретного устройства. Актуально при повышении нагрузки (числа устройств) на контроллер памяти.

Trpre, Read preamble - время, в течение которого контроллер памяти откладывает активацию приема данных перед чтением, во избежание повреждения данных.

Trpst, Twpre, Twpst, Write preamble, read postamble, write postamble - то же для записи и после приема данных.

Read/write Queue Bypass - определяет число раз, которое самый ранний запрос в очереди может быть обойден контроллером памяти, прежде чем быть выполненным.

Bypass Max - определяет, сколько раз самая ранняя запись в DCQ может быть обойдена, прежде чем выбор арбитра будет аннулирован. При установке в 0 выбор арбитра всегда учитывается.

SDRAM MA Wait State, Read Wait State - установка 0-2-тактного опережения адресной информации перед подачей сигнала CS#.

Turn-Around Insertion - задержка между циклами. Добавляет задержку в такт между двумя последовательными операциями чтения/записи.

DRAM R/W Leadoff Timing, rd/wr command delay - задержка перед выполнением команды чтения/записи. Обычно составляет 8/7 или 7/5 тактов соответственно. Время от подачи команды до активации банка.

Speculative Leadoff, SDRAM Speculative Read - Обычно в память поступает сначала адрес, затем команда на чтение. Поскольку на расшифровку адреса уходит относительно много времени, можно применить упреждающий старт, подав адрес и команду подряд, без задержки, что повысит эффективность использования шины и снизит простои.

Twtr Same Bank, Write to Read Turnaround Time for Same Bank - время между прекращением операции записи и подачей команды на чтение в одном банке.

Tfaw, Four Active Windows - минимальное время активности четырех окон (активных строк). Применяется в восьмибанковых устройствах.

Strobe Latency. Задержка при посылке строб-импульса (селекторного импульса).

Memory Refresh Rate. Частота обновления памяти.